OMAPL138EZWTD4 IC MPU OMAP-L1X 456MHZ 361NFBGA

Paramètre de produit

Description

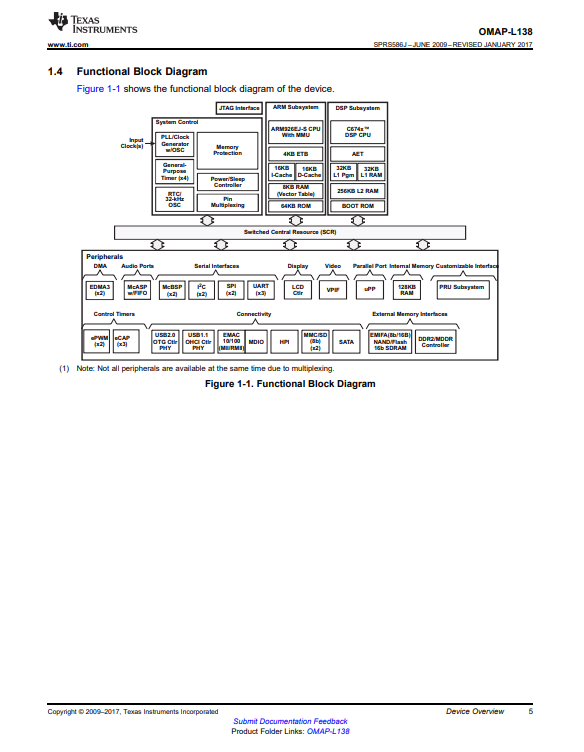

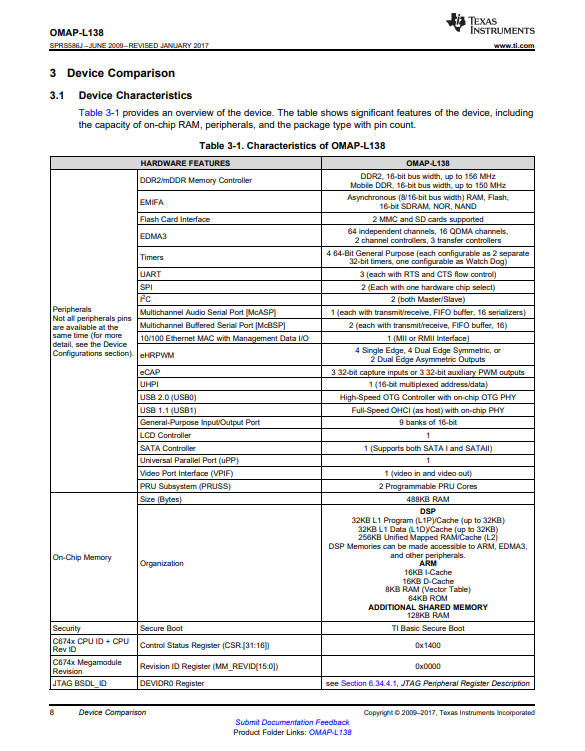

Le processeur OMAP-L138 C6000 DSP+ARM est un processeur d'applications basse consommation basé sur un ARM926EJ-S et un cœur DSP C674x.Ce processeur fournit une puissance nettement inférieure à celle des autres membres de la plate-forme de DSP TMS320C6000™.L'appareil permet aux fabricants d'équipements d'origine (OEM) et aux fabricants de conception originale (ODM) de mettre rapidement sur le marché des appareils dotés de systèmes d'exploitation robustes, d'interfaces utilisateur riches et de performances de processeur élevées grâce à la flexibilité maximale d'une solution de processeur mixte entièrement intégrée.L'architecture double cœur de l'appareil offre les avantages des technologies DSP et d'ordinateur à jeu d'instructions réduit (RISC), incorporant un cœur DSP TMS320C674x hautes performances et un cœur ARM926EJ-S.L'ARM926EJ-S est un cœur de processeur RISC 32 bits qui exécute des instructions 32 bits ou 16 bits et traite des données 32, 16 ou 8 bits.Le cœur utilise le pipelining afin que toutes les parties du processeur et du système de mémoire puissent fonctionner en continu.Le cœur ARM9 possède un coprocesseur 15 (CP15), un module de protection et des unités de gestion de mémoire de données et de programme (MMU) avec des tampons de recherche de table.Le noyau ARM9 a des instructions séparées de 16 Ko et des caches de données de 16 Ko.Les deux caches sont associatifs à 4 voies avec la balise virtuelle d'index virtuel (VIVT).Le cœur ARM9 dispose également de 8 Ko de RAM (Vector Table) et de 64 Ko de ROM.Le cœur DSP de l'appareil utilise une architecture basée sur le cache à 2 niveaux.Le cache de programme de niveau 1 (L1P) est un cache mappé direct de 32 Ko et le cache de données de niveau 1 (L1D) est un cache associatif à deux voies de 32 Ko.Le cache de programme de niveau 2 (L2P) consiste en un espace mémoire de 256 Ko partagé entre l'espace programme et l'espace de données.La mémoire L2 peut être configurée comme mémoire mappée, cache ou une combinaison des deux.Bien que le DSP L2 soit accessible par l'ARM9 et d'autres hôtes du système, 128 Ko supplémentaires de mémoire partagée RAM sont disponibles pour une utilisation par d'autres hôtes sans affecter les performances DSP.

| Caractéristiques: | |

| Attribut | Valeur |

| Catégorie | Circuits intégrés (CI) |

| Embarqué - Microprocesseurs | |

| Fabricant | Texas Instruments |

| Série | OMAP-L1x |

| Emballer | Plateau |

| Statut de la pièce | Actif |

| Processeur central | ARM926EJ-S |

| Nombre de cœurs/largeur de bus | 1 cœur, 32 bits |

| Vitesse | 456 MHz |

| Co-processeurs/DSP | Traitement de signal;C674x, contrôle du système ;CP15 |

| Contrôleurs RAM | SDRAM |

| Accélération graphique | No |

| Contrôleurs d'affichage et d'interface | LCD |

| Ethernet | 10/100Mbps (1) |

| SATA | SATA 3 Gb/s (1) |

| USB | USB 1.1 + PHY (1), USB 2.0 + PHY (1) |

| Tension - E/S | 1.8V, 3.3V |

| Température de fonctionnement | -40°C ~ 90°C (TJ) |

| Fonctions de sécurité | Sécurité de démarrage, Cryptographie |

| Paquet/caisse | 361-LFBGA |

| Ensemble d'appareils du fournisseur | 361-NFBGA (16x16) |

| Interfaces supplémentaires | HPI, I²C, McASP, McBSP, MMC/SD, SPI, UART |

| Numéro de produit de base | OMAPL138 |

En rapportDES PRODUITS

-

Tél

-

E-mail

-

Skype

-

WhatsApp

WhatsApp