TMS320C6657CZHA IC DSP POINT FIXE/FLOAT 625FCBGA

Paramètre de produit

Description

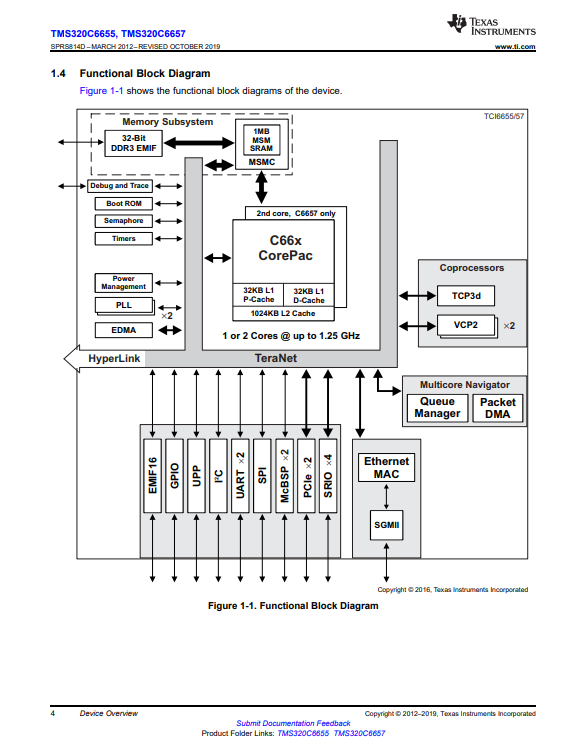

L'architecture KeyStone de TI fournit une plate-forme programmable intégrant divers sous-systèmes (cœurs C66x, sous-système de mémoire, périphériques et accélérateurs) et utilise plusieurs composants et techniques innovants pour maximiser la communication intradispositif et interdispositif qui permet aux différentes ressources DSP de fonctionner de manière efficace et transparente.Au cœur de cette architecture se trouvent des composants clés tels que le navigateur multicœur qui permet une gestion efficace des données entre les différents composants de l'appareil.Le TeraNet est une matrice de commutation non bloquante permettant un mouvement de données interne rapide et sans contention.Le contrôleur de mémoire partagée multicœur permet d'accéder directement à la mémoire partagée et externe sans puiser dans la capacité de la matrice de commutation.Pour une utilisation en virgule fixe, le cœur C66x a 4 fois la capacité de multiplication et d'accumulation (MAC) des cœurs C64x+.De plus, le cœur C66x intègre une capacité en virgule flottante et les performances de calcul brutes par cœur sont à la pointe de l'industrie avec 40 GMACS par cœur et 20 GFLOPS par cœur (fréquence de fonctionnement de 1,25 GHz).Le cœur C66x peut exécuter 8 opérations MAC à virgule flottante simple précision par cycle et peut effectuer des opérations à précision double et mixte et est conforme à la norme IEEE 754.Le cœur C66x intègre 90 nouvelles instructions (par rapport au cœur C64x+) ciblées pour le traitement orienté calcul en virgule flottante et vectoriel.Ces améliorations entraînent des améliorations considérables des performances des noyaux DSP populaires utilisés dans les fonctions de traitement du signal, mathématiques et d'acquisition d'images.Le cœur C66x est rétrocompatible avec les cœurs DSP à virgule fixe et flottante C6000 de la génération précédente de TI, garantissant la portabilité du logiciel et des cycles de développement logiciel raccourcis pour les applications migrant vers un matériel plus rapide.Le DSP C665x intègre une grande quantité de mémoire sur puce.En plus de 32 Ko de programme L1 et de cache de données, 1024 Ko de mémoire dédiée peuvent être configurés en tant que RAM mappée ou cache.L'appareil intègre également 1024 Ko de mémoire partagée multicœur qui peut être utilisée comme SRAM L2 partagée et/ou SRAM L3 partagée.Toutes les mémoires L2 intègrent la détection et la correction d'erreurs.Pour un accès rapide à la mémoire externe, cet appareil comprend une interface de mémoire externe DDR-3 32 bits (EMIF) fonctionnant à un taux de 1333 MHz et prend en charge la DRAM ECC.

| Caractéristiques: | |

| Attribut | Valeur |

| Catégorie | Circuits intégrés (CI) |

| Embarqué - DSP (processeurs de signal numérique) | |

| Fabricant | Texas Instruments |

| Série | TMS320C66x |

| Emballer | Plateau |

| Statut de la pièce | Actif |

| Taper | Virgule fixe/flottante |

| Interface | DDR3, EBI/EMI, Ethernet, McBSP, PCIe, I²C, SPI, UART, UPP |

| Fréquence d'horloge | 1GHz |

| Une mémoire non volatile | ROM (128 Ko) |

| RAM sur puce | 2,06 Mo |

| Tension - E/S | 1.0V, 1.5V, 1.8V |

| Tension - Noyau | 1.00V |

| Température de fonctionnement | -40°C ~ 100°C (TC) |

| Type de montage | Montage en surface |

| Paquet/caisse | 625-BFBGA, FCBGA |

| Ensemble d'appareils du fournisseur | 625-FCBGA (21x21) |

| Numéro de produit de base | TMS320 |

En rapportDES PRODUITS

-

Tél

-

E-mail

-

Skype

-

WhatsApp

WhatsApp