EP1C6Q240C8N CI FPGA 185 E/S 240QFP

Paramètre de produit

Description

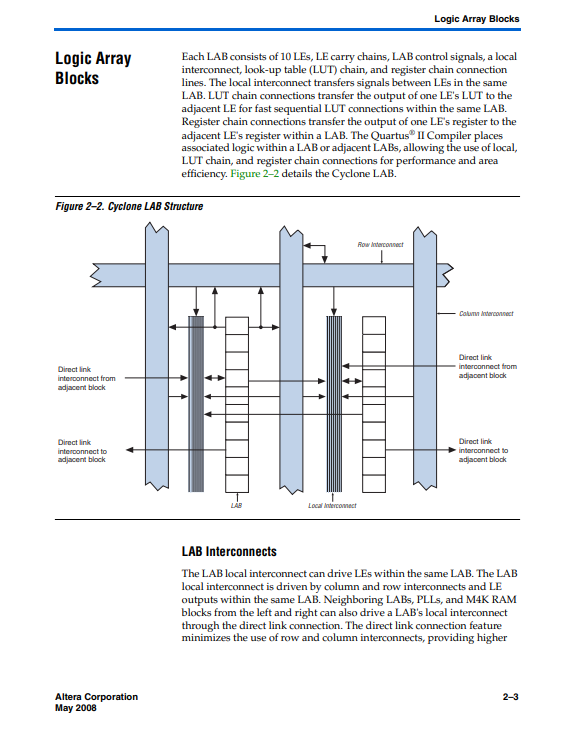

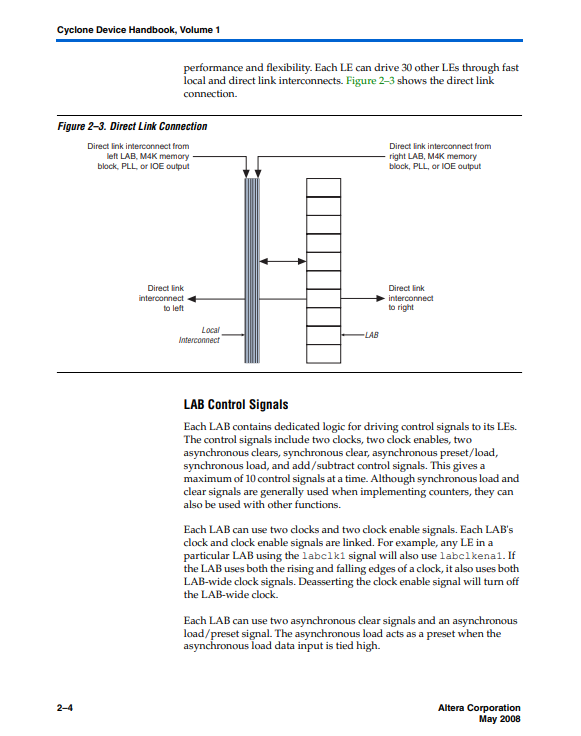

Les dispositifs Cyclone® contiennent une architecture bidimensionnelle basée sur des lignes et des colonnes pour implémenter une logique personnalisée.Les interconnexions de colonnes et de rangées à des vitesses variables fournissent des interconnexions de signaux entre les LAB et les blocs de mémoire intégrés.Le réseau logique se compose de LAB, avec 10 LE dans chaque LAB.Un LE est une petite unité de logique fournissant une implémentation efficace des fonctions logiques de l'utilisateur.Les LAB sont regroupés en lignes et en colonnes sur l'ensemble de l'appareil.Les appareils Cyclone vont de 2 910 à 20 060 LE.Les blocs de RAM M4K sont de véritables blocs de mémoire à double port avec 4K bits de mémoire plus la parité (4 608 bits).Ces blocs fournissent une véritable mémoire dédiée à deux ports, à deux ports simples ou à un seul port jusqu'à 36 bits de large jusqu'à 250 MHz.Ces blocs sont regroupés en colonnes sur l'appareil entre certains LAB.Les appareils Cyclone offrent entre 60 et 288 Kbits de RAM embarquée.Chaque broche d'E/S de l'appareil Cyclone est alimentée par un élément d'E/S (IOE) situé aux extrémités des rangées et des colonnes LAB autour de la périphérie de l'appareil.Les broches d'E/S prennent en charge diverses normes d'E/S asymétriques et différentielles, telles que la norme PCI 66 et 33 MHz, 64 et 32 bits et la norme d'E/S LVDS jusqu'à 640 Mbps.Chaque IOE contient un tampon d'E/S bidirectionnel et trois registres pour enregistrer les signaux d'entrée, de sortie et d'activation de sortie.Les broches DQS, DQ et DM à double usage ainsi que les chaînes à retard (utilisées pour aligner les signaux DDR) fournissent une prise en charge d'interface avec des périphériques de mémoire externes tels que les périphériques DDR SDRAM et FCRAM jusqu'à 133 MHz (266 Mbps).Les dispositifs Cyclone fournissent un réseau d'horloge global et jusqu'à deux PLL.Le réseau d'horloge global se compose de huit lignes d'horloge globales qui alimentent l'ensemble de l'appareil.Le réseau d'horloge global peut fournir des horloges pour toutes les ressources du périphérique, telles que les IOE, les LE et les blocs de mémoire.Les lignes d'horloge globales peuvent également être utilisées pour les signaux de commande.Les PLL Cyclone fournissent une horloge à usage général avec multiplication d'horloge et déphasage ainsi que des sorties externes pour la prise en charge d'E/S différentielles à grande vitesse.

| Caractéristiques: | |

| Attribut | Valeur |

| Catégorie | Circuits intégrés (CI) |

| Embarqué - FPGA (Field Programmable Gate Array) | |

| Fabricant | Intel |

| Série | Cyclone® |

| Emballer | Plateau |

| Statut de la pièce | Obsolète |

| Nombre de LAB/CLB | 598 |

| Nombre d'éléments/cellules logiques | 5980 |

| Nombre total de bits de RAM | 92160 |

| Nombre d'E/S | 185 |

| Tension - Alimentation | 1.425V ~ 1.575V |

| Type de montage | Montage en surface |

| Température de fonctionnement | 0°C ~ 85°C (TJ) |

| Paquet/caisse | 240-BFQFP |

| Ensemble d'appareils du fournisseur | 240-PQFP (32x32) |

| Numéro de produit de base | EP1C6 |

En rapportDES PRODUITS

-

Tél

-

E-mail

-

Skype

-

WhatsApp

WhatsApp