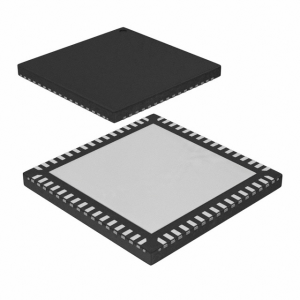

ATXMEGA256A3U-MH IC MCU 8/16BIT 256KB FLASH 64QFN

Paramètre de produit

Description

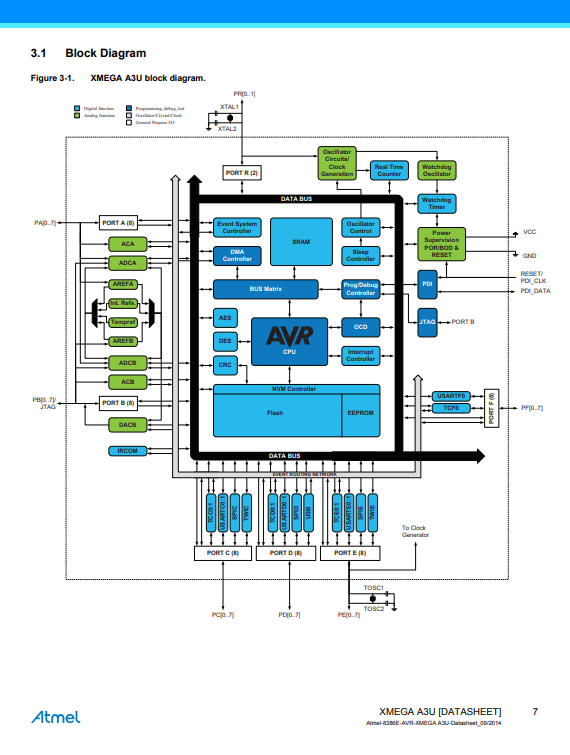

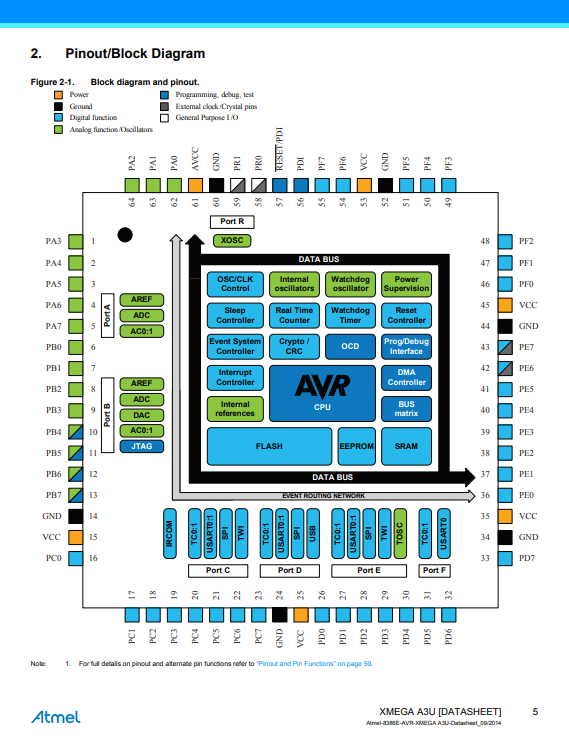

L'Atmel AVR XMEGA est une famille de microcontrôleurs 8/16 bits à faible consommation d'énergie, hautes performances et riches en périphériques basés sur l'architecture RISC améliorée AVR.En exécutant des instructions dans un seul cycle d'horloge, le dispositif AVR XMEGA atteint des débits CPU approchant un million d'instructions par seconde (MIPS) par mégahertz, permettant au concepteur du système d'optimiser la consommation d'énergie par rapport à la vitesse de traitement.Le processeur AVR combine un jeu d'instructions riche avec 32 registres de travail à usage général.Les 32 registres sont directement connectés à l'unité logique arithmétique (ALU), permettant d'accéder à deux registres indépendants en une seule instruction, exécutée en un cycle d'horloge.L'architecture résultante est plus efficace en termes de code tout en atteignant des débits plusieurs fois plus rapides que les microcontrôleurs conventionnels à accumulateur unique ou basés sur CISC.Les appareils AVR XMEGA A3U offrent les fonctionnalités suivantes : mémoire flash programmable intégrée au système avec capacités de lecture pendant l'écriture ;EEPROM et SRAM internes ;contrôleur DMA à quatre canaux, système d'événements à huit canaux et contrôleur d'interruption multiniveau programmable, 50 lignes d'E/S à usage général, compteur en temps réel (RTC) 16 bits ;sept temporisateurs/compteurs 16 bits flexibles avec canaux de comparaison et PWM ;sept USART ;deux interfaces série à deux fils (TWI);une interface USB 2.0 pleine vitesse ;trois interfaces périphériques série (SPI);Moteur cryptographique AES et DES ;deux ADC 16 canaux, 12 bits avec gain programmable ;un DAC 12 bits à 2 canaux ;quatre comparateurs analogiques (CA) avec mode fenêtre ;minuterie de chien de garde programmable avec oscillateur interne séparé ;oscillateurs internes précis avec PLL et prescaler ;et détection de baisse de tension programmable.L'interface de programmation et de débogage (PDI), une interface rapide à deux broches pour la programmation et le débogage, est disponible.Les appareils ont également une norme IEEE.Interface JTAG conforme à la norme 1149.1, qui peut également être utilisée pour le balayage périphérique, le débogage sur puce et la programmation.

| Caractéristiques: | |

| Attribut | Valeur |

| Catégorie | Circuits intégrés (CI) |

| Embarqué - Microcontrôleurs | |

| Fabricant | Technologie des micropuces |

| Série | AVR® XMEGA® A3U |

| Emballer | Plateau |

| Statut de la pièce | Actif |

| Processeur central | RAV |

| Taille du noyau | 8/16 bits |

| Vitesse | 32MHz |

| Connectivité | I²C, IrDA, SPI, UART/USART, USB |

| Périphériques | Détection/réinitialisation de la baisse de tension, DMA, POR, PWM, WDT |

| Nombre d'E/S | 50 |

| Taille de la mémoire du programme | 256 Ko (128 Ko x 16) |

| Type de mémoire programme | ÉCLAIR |

| Taille EEPROM | 4K x 8 |

| Taille de la RAM | 16K x 8 |

| Tension - Alimentation (Vcc/Vdd) | 1.6V ~ 3.6V |

| Convertisseurs de données | A/N 16x12b ;D/A 2x12b |

| Type d'oscillateur | Interne |

| Température de fonctionnement | -40°C ~ 85°C (TA) |

| Type de montage | Montage en surface |

| Paquet/caisse | 64-VFQFN Coussin exposé |

| Ensemble d'appareils du fournisseur | 64-QFN (9x9) |

| Numéro de produit de base | ATXMEGA256 |

En rapportDES PRODUITS

-

Tél

-

E-mail

-

Skype

-

WhatsApp

WhatsApp